鄭浩鑫,梁愛梅

(深圳市國微電子有限公司,廣東深圳,518000)

帶隙基準電路是最為常見的電源管理電路之一。它被要求在復雜和惡劣的環境下,依舊可以為系統提供高精度、低噪聲的穩定基準電壓。它為芯片提供直流參考電壓,對電路的性能,如運算放大器、低壓差線性穩壓器、模數轉換器等模塊提供高精度、低噪聲的參考電壓,以確保系統的增益、電源穩定性、采樣精度等性能。1971 年,帶隙基準的電路結構被首次提出[1]。由于雙極型晶體管(Bipolar Junction Transistor, BJT)的基極與發射極的電壓VBE具有負溫度系數,而具有不同發射結面積的BJT 管之間的VBE電壓差ΔVBE具有正溫度系數,將兩者通過一定的比例相加,便可以得到幾乎不隨溫度變化而改變的基準電壓。1973 年,K.E. Kuijk 提出了PNP 集電極直接接地的帶隙基準結構[2],如圖1 所示。運算放大器的使用提高了基準電壓的精度,同時由于集電極節點接地,使得該結構更容易在標準CMOS 工藝中實現,在如今電源管理電路設計中得到了非常廣泛的應用。

圖1 Kuijk 結構的帶隙基準電路圖

結合圖1,由于VX=VY,因此電阻R3兩端的電壓可以寫為:

輸出基準電壓VREF可以寫為:

將VREF對溫度T進行求導,可以得到基準電壓的溫度系數表達式:

其中m為常數,T為絕對溫度,k為玻爾茲曼常數,q為電子的能量,Eg表示硅的帶隙能量,n為雙極型晶體管的比例,R2(t)表示經過修調后選出的R2的阻值。

由式(3)可知,通過調整合適的電阻和BJT 比例,可以得到零溫漂系數的電壓。但在實際芯片制造中,由于電阻、晶體管之間的失配,會導致輸出基準電壓隨溫度產生較大的變化,因此需要對基準電壓進行溫度補償。根據采用的帶隙基準電路結構的不同,可以采用不同的補償方法,如電阻修調補償法[3~4]、IPTAT2補償法[5~8]、指數補償法[9~13]、分段線性補償法[14~17]等。在FPGA 這種超大規模電路設計中,基于互聯邏輯高度可訪問的優點,在帶隙基準電路的設計中,常采用電阻修調補償法,通過設置多個修調(trimming)開關,對基準電壓進行修調,以確保每塊芯片的電源的可靠性,提高芯片的良率。然而隨著工藝的進步和器件尺寸的減小,僅修調電阻有時也無法修正由于失配和工藝偏差造成的基準電壓的誤差,需要有額外的修調技術對基準電壓進行修正。本文基于FPGA 的互聯邏輯特性,設計了一種溫漂變化趨勢與基準電壓相反的補償電流產生電路,對基準電壓進行補償。通過設置多個修調開關,對補償電流的斜率和零溫漂點進行調節,以保證在不同工藝偏差下,均可以通過補償產生高精度的基準電壓。電路的具體結構及其工作原理將在下一章進行闡述。

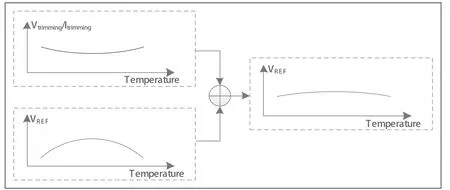

帶隙基準的電路設計中,常將輸出基準電壓的溫度系數在一定的溫度范圍內設計為先增大后減小,呈倒扣碗狀。這能使電阻修調過程中,增大對工藝偏差的容忍度,避免因工藝偏差導致溫漂過大,超出修調范圍。假設能產生一路變化趨勢與基準電壓溫漂系數相反的修調電壓或者電流,如圖2所示,將其注入輸出基準電壓中進行補償,便可以減小輸出基準電壓的溫度系數。

圖2 基準電壓溫度補償原理示意圖

由式1 可知,雙極型晶體管的偏置電流I可以寫為:

將式(4)對溫度T求導,可以得到偏置電流的溫度系數為:

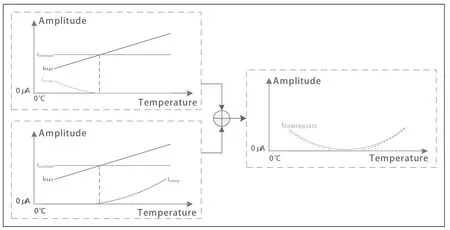

從式(5)可以看出,BJT 的偏置電流實際上是與絕對溫 度 成 正 比(Proportional to absolute temperature,PTAT)的正溫度系數電流IPTAT。假設電流不可為負值,用一路恒定的電流ICONSTANT減去IPTAT,便可以得到隨溫度增大不斷減小的補償電流;

相反的,用IPTAT減去ICONSTANT,便可以得到隨溫度增大不斷增大的補償電流。最后將這兩路電流進行相加,便可以得到具有與基準相反溫漂趨勢的補償電流ICOMPENSATE,如圖3 所示。

圖3 溫度補償電路原理示意圖

基于以上分析,本文提出了一種用于FPGA 的高精度帶隙基準電路,其電路結構圖如圖4 所示,主要由帶隙基準電路,增加驅動能力的輸出緩沖電路(Buffer),溫度補償電流產生電路組成。帶隙基準電路采用經典的Kuijk 結構,PMOS 管PM1為BJT 提供電流偏置。電阻R4有電容C1構成密勒補償電路,提高帶隙基準電路的環路穩定性。PM2鏡像PM1的PTAT 電流至補償電路中,用于產生補償電流。電阻R2是由許多小電阻組成的修調電阻。修調選擇信號作用于數據選擇器(Multiplexer,MUX)上,可以初步修調帶隙基準電壓的溫度系數,將帶隙基準所產生的最小溫漂系數的基準電壓選出并送至緩沖電路B(BufferB)中。BufferB擁有更強的驅動能力,可以更好地驅動下一級電路。另一路修調電壓經過MUX 后輸送至緩沖電路BufferA中。當輸入修調電壓隨溫度變化時,PM3 的源漏電壓也隨之改變。但因為晶體管PM3 工作在飽和區,其輸出電流變化隨溫度變化非常小,相較于PTAT 電流而言,可以視為基本不變的恒定電流。因此采用PM4 鏡像PM3 的輸出電流,輸送至溫度補償電路中,作為與PTAT 電流進行加減的恒定電流。此外,由于PTAT 電流和恒定電流都會因工藝偏差而產生變化,為了使補償電流的溫漂轉折點可以與基準電壓的溫漂轉折點相同,以達到最好的溫度補償效果,BufferA的輸入電壓也通過修調信號和MUX 進行選擇,進而產生不同幅值的恒定電流,如圖4所示。恒定電流可以表示為:

圖4 帶隙基準電路結構示意圖

其中KPn為跨導參數,VGS( t )表示經過trimming 后BufferA的輸出電壓。補償電流注入電阻R9中,對BufferB輸出的電壓進行溫度補償,輸出的基準電壓可以寫為:

圖5 給出了溫度補償電流產生電路圖。NMOS 管NM1-NM12組成多組電流鏡,將IPTAT和ICONSTANT分別鏡像到PMOS 電流鏡組MirrorA和MirrorB中。為了滿足補償電流不為負值這一先決條件,設置了PMOS 電 流 鏡 組MirrorC和MirrorD,分別補充電流鏡A 和B的電流差值。將該電流差值鏡像出來并相加,即可以得到補償電流Icompensate。根據KCL,結合圖5,可以寫出電流鏡C 的電流為:

圖5 溫度補償電流產生電路圖

為了達到最好的溫度補償效果,電流鏡C 和D 采用多組并聯可調的修調方式,將補償電流進行不同比例的鏡像,進而調整補償電流的斜率。因此輸出補償電流ICOMPENSATE可以表示為:

其中k1 和k2 是電流鏡的比例系數。綜上所述,聯立式(2)、式(4)~(10),可以寫出輸出基準電壓的表達式為:

設定n 以及電阻的阻值,并通過改變修調的碼值,改變式(11)中的R2( t ),VGS( t )等各項參數的值,最終可以將輸出基準電壓的溫漂系數修調到最小。

圖6 給出了不同工藝角下,輸出基準電壓補償前后的溫度掃描仿真結果。通過設置合適的修調碼值后,在溫度從-55℃變化到125℃的范圍內,典型工藝角(typical PMOS and typical NMOS, tt)下,輸出基準電壓隨溫度變化范圍從3.5mV 降低到1mV 左右。單個工藝角下,輸出基準電壓的溫度變化范圍不會超過1.25mV。表1給出了全工藝角下,輸出基準電壓的溫漂系數,可以看出溫漂系數不會超過6.5ppm/℃,滿足高精度基準電壓的性能需求。

表1 不同工藝角下,輸出基準電壓的溫漂系數

圖6

實際的芯片生產中,即使由于失配等問題使輸出產生偏差,也可以通過FPGA 的互聯邏輯,改變修調碼值,為運算放大器、低壓差線性穩壓器、模數轉換器等模塊提供穩定、高精度的基準電壓值。此外,在補償的過程中,需要定位基準電壓零溫漂點的大致范圍,再分別調整正負溫漂系數的補償電流的大小進行補償,增大了芯片測試的工作量。在對工藝特性足夠了解后,可以將BufferB輸入電壓的零溫漂點設置在較低溫度或者較高溫度,僅需采用正溫度系數或負溫度系數的補償電流進行補償。在保證芯片良率的同時,進一步降低了芯片的測試成本。

本文基于Kuijk 結構的帶隙基準電路結構,針對FinFET 工藝下工藝偏差造成的基準電壓輸出偏差問題,設計了一種用于FPGA 的可調整補償電流的高精度基準電路。結合FPGA 內部互聯邏輯高度可訪問的特點,采用了電阻修調的方法對輸出基準電壓進行初步修調,再利用溫度補償電路產生拐點和斜率可調整的補償電流,對不同工藝腳下的輸出基準電壓進行精細修調。仿真結果表明,在-55℃~125℃的溫度范圍內,在全工藝角下,輸出基準電壓誤差不超過1.25mV,溫漂系數不超過6.5ppm/℃,可為FPGA 內部其他模塊提供高精度、穩定的偏置電壓。

猜你喜歡基準電阻補償電阻大小誰做主中學生數理化·中考版(2020年10期)2020-11-27無功補償電容器的應用山東冶金(2019年5期)2019-11-16巧測電阻中學生數理化·中考版(2018年11期)2019-01-31電阻焊制造技術與機床(2017年3期)2017-06-23解讀補償心理人生十六七(2016年14期)2016-12-01明基準講方法保看齊公民與法治(2016年19期)2016-05-17基于multisim13.0負電阻在電源中作用的仿真通信電源技術(2016年5期)2016-03-22滑落還是攀爬讀者·校園版(2015年7期)2015-05-14植物補償和超補償作用現代農業(2015年1期)2015-02-28離婚時,能否要求家務補償海峽姐妹(2014年5期)2014-02-27